型号: ZX12232B

2009年3月15日

北京市海淀区中关村大街32号和盛大厦811室 电话:(86)-010-52926620 传真:(86)-010-52926621

企业网站:http://www.zxlcd.com

# **RECORDS OF REVISION**

| DATE                  | REVISED<br>NO. | REVISED DESCRIPTIONS       | PREPARED | CHECKED | APPROVED |

|-----------------------|----------------|----------------------------|----------|---------|----------|

| APR-11-2006           | 1.00           | FIRST ISSUE                | tfb      |         |          |

| September 28,<br>2007 | 1.01           | Amend wrappage and address | ynn      |         |          |

|                       |                |                            |          |         |          |

|                       |                |                            |          |         |          |

|                       |                |                            |          |         |          |

|                       |                |                            |          |         |          |

|                       |                |                            |          |         |          |

|                       |                |                            |          |         |          |

|                       |                |                            |          |         |          |

|                       |                |                            |          |         |          |

|                       |                |                            |          |         |          |

|                       |                |                            |          |         |          |

|                       |                |                            |          |         |          |

# **CONTENTS**

| 1.  | FEATURES                           | 1  |

|-----|------------------------------------|----|

| 2.  | BLOCK DIAGRAM &APPLICATION CIRCUIT | 1  |

| 3.  | OUTLINE DIMENSIONS                 | 3  |

| 4.  | ABSOLUTE MAXIMUM RATING            | 4  |

| 5.  | ELECTRICAL CHARACTERISTICS         | 4  |

| 6.  | OPTICAL CHARACTERISTICS            | 5  |

| 7.  | TIMING CHARACTERISTICS             | 6  |

| 8.  | DISPLAY CONTROL INSTRUCTION        | 8  |

| 9.  | DISPLAY CONTROL FUNCTIONS          | 16 |

| 10. | INTERFACE PIN CONNECTIONS          | 22 |

| 11. | RELIABILITY                        | 24 |

| 12. | QUALITY GUARANTEE                  | 25 |

| 13. | INSPECTION CRITERIA                | 26 |

| 14. | PRECAUTIONS FOR USING LCD MODULES  | 27 |

| 15. | USING LCD MODULES                  | 28 |

# 1. FEATURES:

| ITEM                   | STANDARD VALUE                              | UNIT |

|------------------------|---------------------------------------------|------|

| Display Type           | 122* 32dots                                 | -    |

| LCD Type               | □STN, BLUE, Transflective, Negative         | -    |

|                        | ■STN, YELLOW-GREEN, Transflective, Position |      |

|                        | ☐STN, GREY, Transflective, Negative         |      |

|                        | □FSTN,, Transflective, Position,            |      |

| LCD Duty               | 1/16                                        | -    |

| LCD Bias               | 1/5                                         | -    |

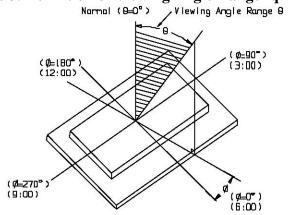

| Viewing Direction      | 6:00                                        | -    |

| Backlight Type         | □S-LEDL(BLUE)                               | -    |

|                        | ■L-LEDL(YELLOW_GREEN)                       |      |

|                        | □S-LED(White)                               |      |

| Interface              | 6800 Series or 8080 series                  | -    |

| Driver IC              | SED1520                                     | -    |

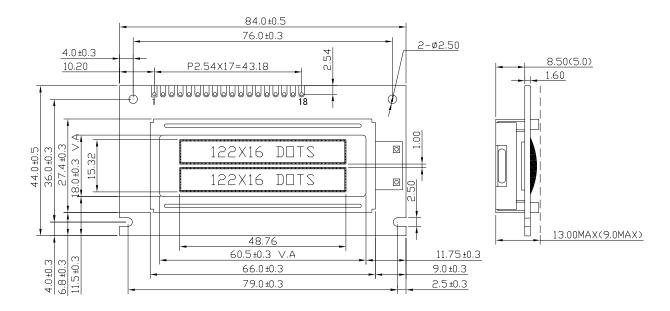

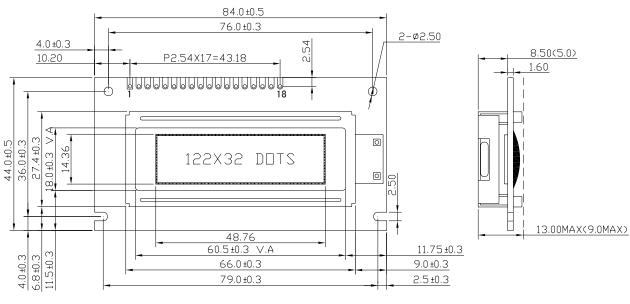

| Module Dimension       | 84.0(W) X44.0(H) X13.0 (MAX)(T)             | mm   |

| Effective Display Area | 48.76 (W) X15.32 (H)                        | mm   |

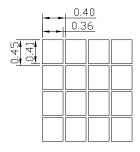

| Dot Size               | 0.36 (W) X 0.41 (H)                         | mm   |

| Dot Pitch              | 0.40W) X 0.45 (H)                           | mm   |

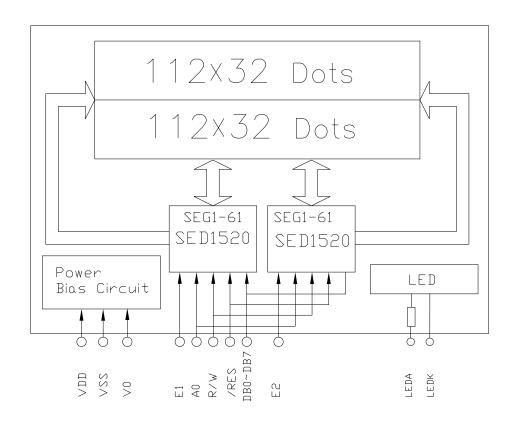

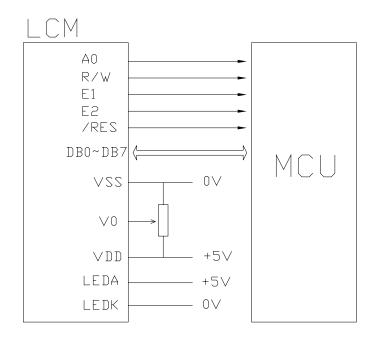

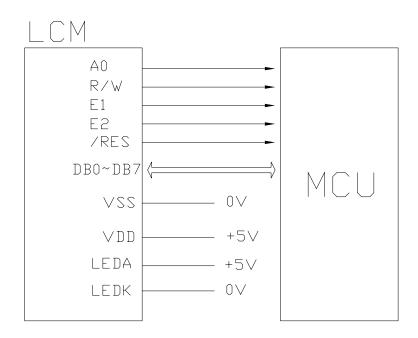

# 2. BLOCK DIAGRAM & APPLICATION CIRCUIT:

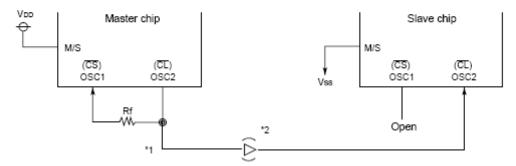

# **Application For Adjustable Contrast**

# **Application For Immovable Contrast**

# 3. OUTLINE DIMENSIONS

LCM<sub>1</sub>

LCM 2

# 4. ABSOLUTE MAXIMUM RATING

| ITEM                            | SYMBOL         | CONDITION  | STA  | VALUE | UNIT    |                      |

|---------------------------------|----------------|------------|------|-------|---------|----------------------|

| I I E IVI                       | STIVIDOL       | CONDITION  | MIN  | TYP   | MAX     | CIVIT                |

| POWER SUPPLY FOR LOGIC          | VDD            | Ta=25°C    | -0.3 | -     | 8.0     | V                    |

| INPUT VOLTAGE                   | VIN            | Ta=25°C    | -0.3 | -     | VDD+0.3 | V                    |

| Module OPERATION TEMPERATURE    | TOPR           | LCM 1      | -20  |       | +70     | °C                   |

| Wildule Of ENATION TEMILENATURE | TOPK           | LCM 2      | -10  | _     | +60     | C                    |

| Module STORAGE TEMPERATURE      | TSTG           | LCM 1      | -30  | -     | +80     | $^{\circ}\mathrm{C}$ |

| WOULD STORAGE LEWIPERATURE      | 1316           | LCM 2      | -20  | -     | +70     |                      |

| Storage Humidity                | H <sub>D</sub> | Ta < 40 °C | -    |       | 90      | %RH                  |

# 5. ELECTRICAL CHARACTERISTICS

| ITEM                   | SYMBOL  | CONDITION           | MIN     | TYP  | MAX     | UNIT |

|------------------------|---------|---------------------|---------|------|---------|------|

| Supply Voltage (logic) | VDD-VSS | -                   | 4.5     | 5    | 5.5     | V    |

| Supply Voltage (LCD)   | VDD-V0  | Ta=+25°C            | -       | 5    | -       | V    |

| Innut gional voltage   | V-IH    | "H" level           | 0.8 VDD | -    | VDD     | V    |

| Input signal voltage   | V-IL    | "L" level           | VSS     | -    | 0.2 VDD | V    |

| Output signal valtage  | V-OH    | "H" level           | 0.5 VDD | -    | -       | V    |

| Output signal voltage  | VOL     | "H" level           | -       | -    | 0.1VDD  | V    |

| Supply Current (logic) | IDD     | VDD=5.0V            | -       | 0.12 | -       | mA   |

|                        |         | LED(White)          |         | 3.1  |         |      |

| Backlight Voltage      | V-BL    | L-LED(Yellow-Green) | -       | 4.1  | -       | V    |

|                        |         | LED(Blue)           |         | 0.06 |         |      |

|                        |         | LED(White)          |         | 40   |         |      |

| Backlight Current      | I-BL    | L-LED(Yellow-Green) | -       | 80   | -       | mA   |

|                        |         | LED(Blue)           |         | 40   | -       |      |

| Backlight Driver Wave  |         |                     |         |      |         | kHz  |

| Backlight Brightness   |         |                     |         |      |         |      |

| Backlight Life Time    |         |                     |         |      |         |      |

# 6. OPTICAL CHARACTERISTICS

| Item           | Symbol | Condition | Min | Тур | Max | Unit | Remarks         | Note |

|----------------|--------|-----------|-----|-----|-----|------|-----------------|------|

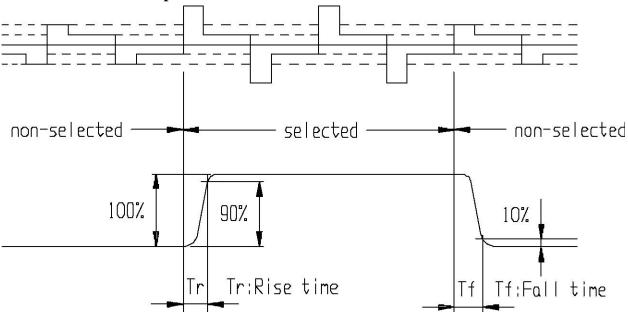

| Response       | Tr     | -         | -   | 140 | -   | ms   | -               | 1    |

| Time           | Tf     | -         | -   | 133 | -   | ms   | -               | 1    |

| Contrast Ratio | Cr     | -         | -   | 5.1 | -   | -    | -               | 2    |

| <b>17</b>      |        |           | 41  | -   | -   | deg  | Ø= 90           | 3    |

| Viewing        | θ      | Cr≥ 2     | 38  | -   | -   | deg  | Ø = 270         | 3    |

| Angle<br>Range |        |           | 32  | -   | -   | deg  | $\emptyset = 0$ | 3    |

| Kange          |        |           | 19  | -   | -   | deg  | Ø = 180         | 3    |

Note 1. Definition of response time

Note 2. Definition of Contrast Ratio 'Cr'

Brightness of non-selected segment(82)

Brightness of selected segment(Bl)

Brightness curve for non-selected segment

Brightness curve for selected segment

Orlving Voltage

Note 3. Definition of Viewing Angle Range 'q'

# 7. TIMING CHARACTERISTICS

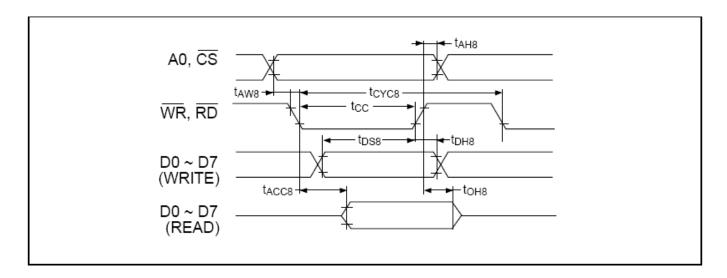

# 7.1 System Bus Read/Write (8080 family)

Ta = -20 to 75°C, Vss =  $-5.0V \pm 10\%$ , Unit: ns

| Signal | Symbol | Parameter           | Min. | Max. | Condition  |

|--------|--------|---------------------|------|------|------------|

| A0, CS | t AH8  | Address hold time   | 10   |      |            |

| A0, C5 | t AW8  | Address setup time  | 20   |      |            |

| WR, RD | t cycs | System cycle time   | 1000 |      |            |

| WK, KD | t cc   | Control pulse width | 200  |      |            |

|        | t DS8  | Data setup time     | 80   |      |            |

| D0 D7  | t DH8  | Data hold time      | 10   |      |            |

| D0-D7  | t ACC8 | RD access time      |      | 90   | CL = 100pF |

|        | t OH8  | Output disable time | 10   | 60   |            |

<sup>\*1.</sup> Each of the values where Vss = -3.0V is about 200% of that where Vss = -5.0V (i.e., the listed value).

<sup>\*2.</sup> The rise or fall time of input signals should be less than 15 ns.

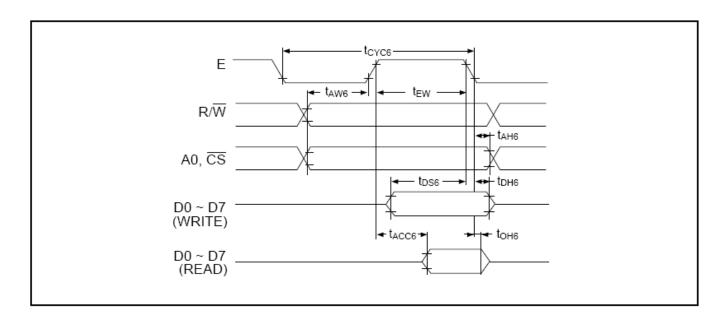

# 7.2 System Bus Read/Write (6800 family)

Ta = -20 to 75°C, Vss = -5.0V  $\pm$  10%, Unit: ns

| Signal | Symbol   | Parameter               | Min.            | Max. | Condition |            |

|--------|----------|-------------------------|-----------------|------|-----------|------------|

| A0, CS | t cyc6*1 | System cycle time       |                 | 1000 |           |            |

| R/W    | t AW6    | Address setup time      |                 | 20   |           |            |

|        | t AH6    | Address hold time       |                 | 10   |           |            |

| D0-D7  | t DS6    | Data setup time         | Data setup time |      |           |            |

|        | t DH6    | Data hold time          |                 | 10   |           |            |

|        | tOH6     | Output disable time     |                 | 10   | 60        | CL = 100pF |

|        | t ACC6   | Access time             | Access time     |      |           |            |

| E      | t EW     | Enable pulse width Read |                 | 100  |           |            |

|        |          |                         | Write           | 80   |           |            |

<sup>\*1.</sup> It cycs indicates the cycle time during which CS•E = "H". It does not mean the cycle time of signal E.

<sup>\*2.</sup> Each of the values where Vss = -3.0V is about 200% of that where Vss = -5.0V (i.e., the listed value).

<sup>\*3.</sup> The rise or fall time of input signals should be less than 15 ns.

# 8. Display Control Instruction

# Please Consult SED1520 Data Sheet

Table 3 lists the commands used with the SED1520. This LSI uses a combination of A0, R/W ( $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ ) to identify a data bus signal. Interpretation and execution of a command depends not on external clock but on internal timing alone. Therefore, a command can be executed so fast that no busy check is needed.

A detailed description of commands follows.

### 8.1 DISPLAY ON/OFF

This command forces all display to turn on or off.

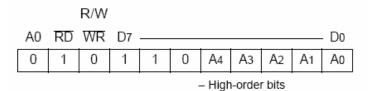

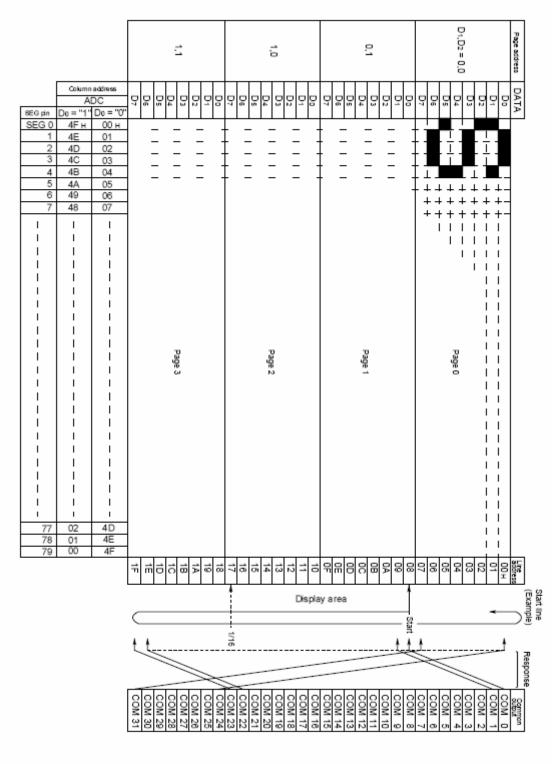

# 8.2 DISPLAY START LINE

This command specifies a line address (shown in Fig. 2.3.8.1) thus marking the display line that corresponds to COM0. Display begins with the specified line address and covers as many lines as match the display duty in address ascending order. Dynamic line address change with the Display Start Line command enables column-wise scrolling or page change.

|   | A4 | А3 | A2 | A1 | A0 | Line address |

|---|----|----|----|----|----|--------------|

| Γ | 0  | 0  | 0  | 0  | 0  | 0            |

|   | 0  | 0  | 0  | 0  | 1  | 1            |

|   |    |    | _  |    |    | _            |

|   |    |    | _  |    |    | _            |

|   | 1  | 1  | 1  | 1  | 1  | 31           |

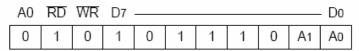

# 8.3 SET PAGE ADDRESS

This command is used to specify a page address equivalent to a row address for MPU access to the display data RAM. A required bit of the display data RAM can be accessed by specifying its page address and column address. Changing the page address causes no change in display.

R/W

| A1 | A0 | Page |

|----|----|------|

| 0  | 0  | 0    |

| 0  | 1  | 1    |

| 1  | 0  | 2    |

| 1  | 1  | 3    |

# 8.4 COLUMN ADDRESS

This command specifies a display data RAM column address. The column address is incremented by 1 each time the MPU accesses from the set address to the display data RAM. Thus, it is possible for the MPU to gain continuous access to only the data. This incrementing stops with address 80; the page address is not continuously changed.

R/W

| Α0 | $\overline{\text{RD}}$ | $\overline{\text{WR}}$ | D7 |    |    |    |    |    |    | D0 |

|----|------------------------|------------------------|----|----|----|----|----|----|----|----|

| 0  | 1                      | 0                      | 0  | A6 | A5 | A4 | Аз | A2 | A1 | Ao |

| A6 | Α5 | A4 | А3 | A2 | <b>A</b> 1 | A0 | Column address |

|----|----|----|----|----|------------|----|----------------|

| 0  | 0  | 0  | 0  | 0  | 0          | 0  | 0              |

| 0  | 0  | 0  | 0  | 0  | 0          | 1  | 1              |

|    |    |    | _  |    |            |    | _              |

|    |    |    | _  |    |            |    | _              |

| 1  | 0  | 0  | 1  | 1  | 1          | 1  | 79             |

### 8.5 READ STATUS

R/W

| , ,, |   | WR |      |     |            |       |   |   |   | D0 |

|------|---|----|------|-----|------------|-------|---|---|---|----|

| 0    | 0 | 1  | Busy | ADC | ON/<br>OFF | Reset | 0 | 0 | 0 | 0  |

BUSY: BUSY being "1" means that system is performing an internal operation or is reset. No

command is accepted before BUSY = "0". As long as the cycle time requirement is met,

no BUSY check is needed.

ADC: Indicates assignment of column addresses to segment drivers.

0: Inverted (column address 79-n ↔ segment driver n)

1: Forward (column address n ↔ segment driver n)

ON/OFF: Indicates display on or off.

0: Display on

1: Display off

This bit has polarity reverse to the Display ON/OFF command.

RESET: Indicates that system is being initialized by the RES signal or the Reset command.

0: Display mode

1: Being reset

### 8.6 WRITE DISPLAY DATA

This command allows the MPU to write 8 bits of data into the display data RAM. Once the data is written, the column address is automatically incremented by 1; this enables the MPU to write multiword data continuously.

R/W

| Α0 | RD | WR | D7 | D0         |

|----|----|----|----|------------|

| 1  | 1  | 0  |    | Write data |

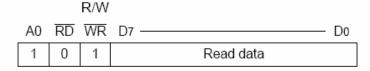

### 8.7 READ DISPLAY DATA

This command allows the MPU to read 8 bits of data from the display data RAM location specified by a column address and a page address. Once the data is read, the column address is automatically incremented by 1; this enables the MPU to read multi-word data continuously.

A dummy read is needed immediately after the column address is set. For details, see 3. (1)–(c).??

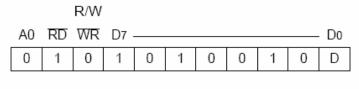

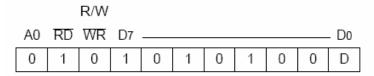

# 8.8 SELECT ADC

This command inverts the relation of assignment between display data RAM column addresses and segment driver outputs. In other words, the Select ADC command can software-invert the order of segment driver output pins, reducing the restrictions on the configuration of ICs at LCD module assembly. For details, see Fig. 2.3.8.1.

Incrementing the column address by 1, which takes place after the MPU writing or reading display data, follows the sequence of column addresses specified in Fig. 2.3.8.1.

| Α0 | RD | WR | D7 - |   |   |   |   |   |   | D0 |

|----|----|----|------|---|---|---|---|---|---|----|

| 0  | 1  | 0  | 1    | 0 | 1 | 0 | 0 | 0 | 0 | D  |

D = 0: Clockwise output (forward)

D = 1: Counterclockwise output (reverse)

# 8.9 STATIC DRIVE ON/OFF

This command forces all display to be on and, at the same time, all common output to be selected.

D = 0: Static drive off D = 1: Static drive on

### 8.10 SELECT DUTY

This command is used to select the duty (degree of multiplexity) of LCD driving. It is valid for the SED1520F (actively operating LSI) only, not valid for the SED1521F (passively operating LSI). The SED1521F operates with any duty determined by the FR signal.

D = 0: Duty 1/16 D = 1: Duty 1/32

If the system contains both SED1520FOA (internal oscillation) and the SED1521FOA LSIs, they must have the same duty.

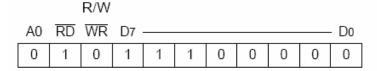

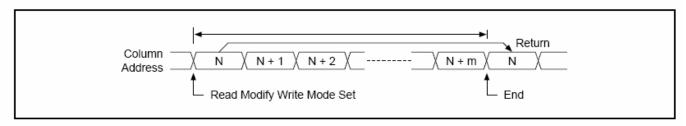

### 8.11 READ MODIFY WRITE

This command is used with the End command in a pair. Once it has been entered, the column address will be incremented not by the Read Display Data command but by the Write Display Data command only. This mode will stay until the End command is entered.

Entry of the End command causes the column address to return to the address which was valid when the Read Modify Write command was entered. This function lessens the load of the MPU when the data in a specific display area are repeatedly updated (as blinking cursor).

Even in the Read Modify Write mode, any command other than Read/Write Data and Set Column Address may be used.

# 8..11.1 Cursor Blinking Sequence

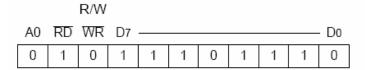

# 8.12 END

This command cancels the Read Modify Write command, returning the column address to the initial mode address.

# 8.12.1 End Timing

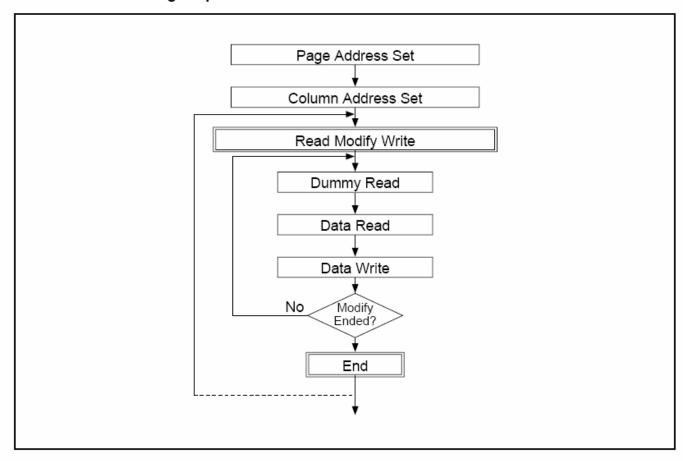

### 8.13 **RESET**

This command initializes the display start line register, column address counter, and page address counter without any effect on the display data RAM. For details, see section 2.3.12.

The reset operation follows entry of the Reset command.

|    |    | R/W |    |   |   |   |   |   |   |      |

|----|----|-----|----|---|---|---|---|---|---|------|

| Α0 | RD | WR  | D7 |   |   |   |   |   |   | - Do |

| 0  | 1  | 0   | 1  | 1 | 1 | 0 | 0 | 0 | 1 | 0    |

Initialization at power-on is performed not by the Reset command but by a reset signal applied to the RES pin.

# 8.14 SAVE POWER (COMBINED COMMAND)

Static drive going on with display off invokes power-saving mode, reducing current consumption to nearly static current level. During this mode, the SED1520 holds the following conditions:

- (a) It stops driving the LCD; the segment and common driver outputs are at VDD level.

- (b) Oscillation and external clock input are disabled; OSC2 is in floating condition.

- (c) The display data and operational mode are held.

The power-saving mode is cancelled by display on or static drive off.

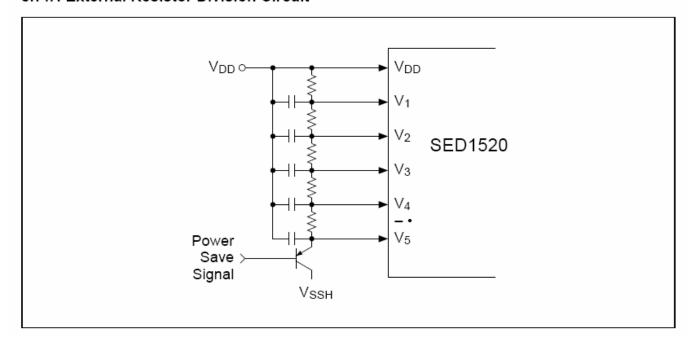

If an external resistor division circuit is used to give LCD driving voltage level, the current flowing into the resistors must be cut off by the power-save signal.

### 8.14.1 External Resistor Division Circuit

Table 3 Commands

|      | Command                         |    |    |    |      | 0   | ode    | ,     |       |               |      |            | E.                                                                                                                        | unction                                                                                                    |

|------|---------------------------------|----|----|----|------|-----|--------|-------|-------|---------------|------|------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|      | Command                         | A0 | RD | WR | D7   | D6  | D5     | D4    | D3    | D2            | D1   | D0         | -                                                                                                                         | inction                                                                                                    |

| (1)  | Display ON/OFF                  | 0  | 1  | 0  | 1    | 0   | 1      | 0     | 1     | 1             | 1    | 0/1        | play RAM data or intel<br>1: ON                                                                                           | off, independently of dis-<br>rnal status.<br>mode with static drive on)*                                  |

| (2)  | Display start line              | 0  | 1  | 0  | 1    | 1   | 0      | Disp  |       | Start<br>0–31 |      | ress       | Specifies RAM line co<br>line (COM0) of display                                                                           | rresponding to uppermost                                                                                   |

| (3)  | Set page address                | 0  | 1  | 0  | 1    | 0   | 1      | 1     | 1     | 0             |      | ige<br>-3) | Sets display RAM pag                                                                                                      | e in page address register.                                                                                |

| (4)  | Set column<br>(segment) address | 0  | 1  | 0  | 0    | (   | Colu   | mn A  | ddre  | ess ((        | 0–79 | )          | Sets display RAM colu<br>address register.                                                                                | umn address in column                                                                                      |

| (5)  | Read status                     | 0  | 0  | 1  | Busy | ADC | ON/OFF | RESET | 0     | 0             | 0    | 0          | ADC 1: CW outp<br>0: CCW ou<br>ON/OFF 1: Display                                                                          | atus:<br>operation, 0: Ready<br>out (forward),<br>itput (reverse)<br>off, 0: Display on<br>eset, 0: Normal |

| (6)  | Write display data              | 1  | 1  | 0  |      | •   | ١      | Write | Dat   | а             |      |            | Writes data from<br>data bus into<br>display RAM.                                                                         | Display RAM location<br>whose address has been<br>preset is accessed. After                                |

| (7)  | Read display data               | 1  | 0  | 1  |      |     | ı      | Read  | l Dat | а             |      |            | Reads data from<br>display RAM onto<br>data bus.                                                                          | access, the column<br>address is incremented<br>by 1.                                                      |

| (8)  | Select ADC                      | 0  | 1  | 0  | 1    | 0   | 1      | 0     | 0     | 0             | 0    | 0/1        | Used to invert relation<br>between display RAM<br>segment driver output<br>0: CW output (forward<br>1: CCW output (revers | column addresses and<br>s.<br>)                                                                            |

| (9)  | Static drive ON/<br>OFF         | 0  | 1  | 0  | 1    | 0   | 1      | 0     | 0     | 1             | 0    | 0/1        | Selects normal display  1: Static drive (power- 0: Normal driving                                                         | y or static driving operation.<br>saving mode)                                                             |

| (10) | Select duty                     | 0  | 1  | 0  | 1    | 0   | 1      | 0     | 1     | 0             | 0    | 0/1        | Selects LCD cell drivin<br>1: 1/32<br>0: 1/16                                                                             | ng duty.                                                                                                   |

| (11) | Read modify write               | 0  | 1  | 0  | 1    | 1   | 1      | 0     | 0     | 0             | 0    | 0          |                                                                                                                           | dress counter by 1 when<br>. (This is not done when                                                        |

| (12) | End                             | 0  | 1  | 0  | 1    | 1   | 1      | 0     | 1     | 1             | 1    | 0          | Clears read modify wr                                                                                                     | ite mode.                                                                                                  |

| (13) | Reset                           | 0  | 1  | 0  | 1    | 1   | 1      | 0     | 0     | 0             | 1    | 0          |                                                                                                                           | register on the first line.<br>ress counter and page                                                       |

<sup>\*</sup> With display off (command (1)), static drive going on (9) invokes power-saving mode.

# 9. DISPLAY CONTROL FUNCTIONS

### System Bus

#### MPU interface

Selecting an interface type

The SED1520 series transfers data via 8-bit bidirectional data buses (D0 to D7). As its Reset pin has the MPU interface select function, the 80-series MPU or the 68-series MPU can directly be connected to the

MPU bus by the selection of high or low RES signal

level after reset (see Table 1).

When the CS signal is high, the SED1520 series is disconnected from the MPU bus and set to stand by. However, the reset signal is entered regardless of the internal setup status.

#### Table 1

| RES signal inp | out level MPU type | A0 | E  | R/W | C <b>S</b> | D0 to D7 |

|----------------|--------------------|----|----|-----|------------|----------|

| Active         | 68-series          | 1  | 1  | 1   | 1          | 1        |

| Active         | 80-series          | 1  | RD | WR  | 1          | 1        |

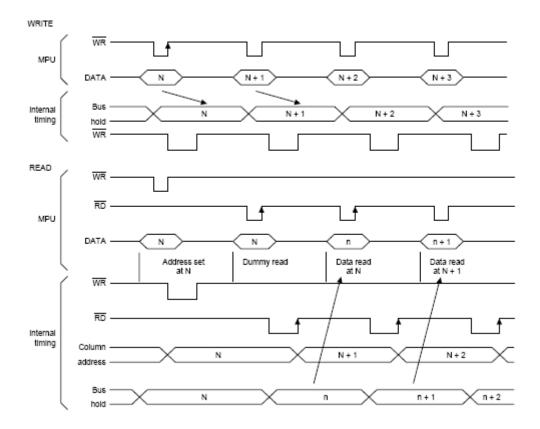

#### Data transfer

The SED1520 and SED1521 drivers use the A0, E (or RD) and R/W (or WR) signals to transfer data between the system MPU and internal registers. The combinations used are given in the table blow.

In order to match the timing requirements of the MPU with those of the display data RAM and control registers all data is latched into and out of the driver. This introduces a one cycle delay between a read request for data and the data arriving. For example when the MPU

executes a read cycle to access display RAM the current contents of the latch are placed on the system data bus while the desired contents of the display RAM are moved into the latch.

This means that a dummy read cycle has to be executed at the start of every series of reads. See Figure 1. No dummy cycle is required at the start of a series of

No dummy cycle is required at the start of a series of writes as data is transferred automatically from the input latch to its destination.

| Common | 68 MPU | 80 M | ИPU | Function                             |

|--------|--------|------|-----|--------------------------------------|

| A0     | R/W    | RD   | WR  | Function                             |

| 1      | 1      | 0    | 1   | Read display data                    |

| 1      | 0      | 1    | 0   | Write display data                   |

| 0      | 1      | 0    | 1   | Read status                          |

| 0      | 0      | 1    | 0   | Write to internal register (command) |

Figure 1 Bus Buffer Delay

### Busy flag

When the Busy flag is logical 1, the SED1520 series is executing its internal operations. Any command other than Status Read is rejected during this time. The Busy flag is output at pin D7 by the Status Read command. If an appropriate cycle time (tcyc) is given, this flag needs not be checked at the beginning of each command and, therefore, the MPU processing capacity can greatly be enhanced.

# Display Start Line and Line Count Registers

The contents of this register form a pointer to a line of data in display data RAM corresponding to the first line of the display (COM0), and are set by the Display Start Line command. See section 3.

The contents of the display start line register are copied into the line count register at the start of every frame, that is on each edge of FR. The line count register is incremented by the CL clock once for every display line, thus generating a pointer to the current line of data, in display data RAM, being transferred to the segment driver circuits.

#### Column Address Counter

The column address counter is a 7-bit presettable counter that supplies the column address for MPU access to the display data RAM. See Figure 2. The counter is incremented by one every time the driver receives a Read or Write Display Data command. Addresses above 50H are invalid, and the counter will not increment past this value. The contents of the column address counter are set with the Set Column Address command.

#### Page Register

The page resiter is a 2-bit register that supplies the page address for MPU access to the display data RAM. See Figure 2. The contents of the page register are set by the Set Page Register command.

# Display Data RAM

The display data RAM stores the LCD display data, on a 1-bit per pixel basis. The relation-ship between display data, display address and the display is shown in Figure 2.

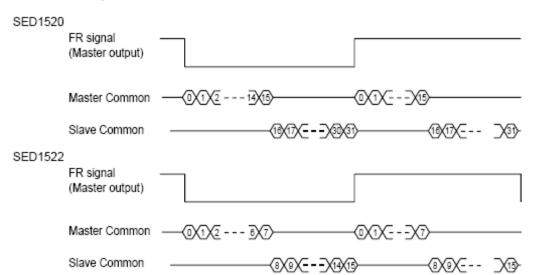

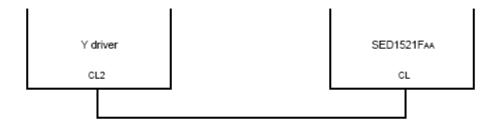

#### Common Timing Generator Circuit

Generates common timing signals and FR frame signals from the CL basic clock. The 1/16 or 1/32 duty (for SED1520) or 1/8 or 1/16 duty (for SED1522) can be selected by the Duty Select command. If the 1/32 duty is selected for the SED1520 and 1/16 duty is selected for the SED1522, the 1/32 and 1/16 duties are provided by two chips consisting of the master and slave chips in the common multi-chip mode.

# Display Data Latch Circuit

This latch stores one line of display data for use by the LCD driver interface circuitry. The output of this latch is controlled by the Display ON/OFF and Static Drive ON/OFF commands.

#### LCD Driver Circuit

The LCD driver circuitry generates the 80 4-level signals used to drive the LCD panel, using output from the display data latch and the common timing generator circuitry.

# Display Timing Generator

This circuit generates the internal display timing signal using the basic clock, CL, and the frame signals, FR. FR is used to generate the dual frame AC-drive waveform (type B drive) and to lock the line counter and common timing generator to the system frame rate. CL is used to lock the line counter to the system line scan rate. If a system uses both SED1520s or SED1522 and SED1521s they must have the same CL frequency rating.

### Oscillator Circuit (SED1520\*0A Only)

A low power-consumption CR oscillator for adjusting the oscillation frequency using Rf oscillation resistor only. This circuit generates a display timing signal. Some of SED1520 and SED1522 series models have a built-in oscillator and others use an external clock. This difference must be checked before use.

Connect the Rf oscillation resistor as follows. To suppress the built-in oscillator circuit and drive the MPU using an external clock, enter the clock having the same phase as the OSC2 of mater chip into OSC2 of the slave chip.

· MPU having a built-in oscillator

- \*1 If the parasitic capacitance of this section increases, the oscillation frequency may shift to the lower frequency. Therefore, the Rf oscillation frequency must be reduced below the specified level.

- \*2 A CMOS buffer is required if the oscillation circuit is connected to two or more slave MPU chips.

- · MPU driven with an external clock

# Reset Circuit

Detects a rising or falling edge of an RES input and initializes the MPU during power-on.

- Initialization status

- Display is off.

- Display start line register is set to line 1.

- Static drive is turned off.

- Column address counter is set to address 0.

- Page address register is set to page 3.

- 1/32 duty (SEDI 520) or 1/16 duty (SEDI 522) is selected.

- Forward ADC is selected (ADC command D0 is 1 and ADC status flag is 1).

- Read-modify-write is turned off.

The input signal level at RES pin is sensed, and an MPU interface mode is selected as shown on Table 1. For the 80-series MPU, the RES input is passed through the inverter and the active high reset signal must be entered. For the 68-series MPU, the active low reset signal must be entered.

As shown for the MPU interface (reference example), the  $\overline{RES}$  pin must be connected to the Reset pin and reset at the same time as the MPU initialization.

If the MPU is not initialized by the use of RES pin during power-on, an unrecoverable MPU failure may occur.

When the Reset command is issued, initialization

Figure 2 Display Data RAM Addressing

1/5 bias, 1/16 duty 1/6 bias, 1/32 duty Voo - Vss Voo V1 ٧2 COMO V3 ٧4 ۷5 Voo V1 COM1 - V2 COM2 V3 COM3 ۷4 COM4 -٧5 COM5 -Voo COM6 - V1 - V2 COM7 COM2 ٧3 ٧4 COM8 -۷5 COM9 -COM10 -Voo V1 COM11 -- V2 COM12 -V3 SEG0 COM13 -- V4 COM14 -٧5 COM15 -Voo - V1 SEG2 SEG3 SEG4 - V2 SEG1 V3 ۷4 ۷5 ۷5 ٧4 - V3 ٧2 V1 COM0-SEG0 Voo -V1 -V2 - -V3 -V4 -V5 ۷5 - V4 V3 ٧2 - V1 COM0-SEG1 - Voo - -V1 - -V2 - -V3 - -V4 - -V5

Figure 4 LCD drive waveforms example

# 11. INTERFACE PIN CONNECTIONS

# CN1 (SED1335 Controller)

| PIN      | SYMBOL     | I/O  | FUNCTION                                                                                                                                                                                                                                                                                  |

|----------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | VDD        | I    | Ground pin, connected to 0V                                                                                                                                                                                                                                                               |

| 2        | VSS        | ı    | Power supply pin for logic .(+5V)                                                                                                                                                                                                                                                         |

| 3        | V0         | I    | Contrast control (VDD~VOUT)                                                                                                                                                                                                                                                               |

| 4        | /RES       | I    | When the /RES signal goes The 6800-series MPU is initialized, and when it                                                                                                                                                                                                                 |

|          |            |      | goes ——, the 8080-series MPU is initialized. The system is reset during edge sense of the /RES signal. The interface type to the 6800-series or 8080-series MPU is selected by the level input as follows:  High level: 6800-series MPU interface.  Low level: 8080-series MPU interface. |

| 5        | E1         | 1    | Chip1:                                                                                                                                                                                                                                                                                    |

|          |            | •    | If the 6800-series MPU is connected:  Used as an enable clock input of the 6800-series MPU.                                                                                                                                                                                               |

|          |            |      | If the 8080-series MPU is connected:                                                                                                                                                                                                                                                      |

|          |            |      | The /RD signal of the 8080-series MPU is entered in this pin. When this signal is kept                                                                                                                                                                                                    |

|          |            |      | low, the SED1520 data bus is in the output status.                                                                                                                                                                                                                                        |

| 6        | E2         | I    | Chip2:                                                                                                                                                                                                                                                                                    |

|          |            |      | If the 6800-series MPU is connected:                                                                                                                                                                                                                                                      |

|          |            |      | Used as an enable clock input of the 6800-series MPU.                                                                                                                                                                                                                                     |

|          |            |      | If the 8080-series MPU is connected:                                                                                                                                                                                                                                                      |

|          |            |      | The /RD signal of the 8080-series MPU is entered in this pin. When this signal is kept low, the SED1520 data bus is in the output status.                                                                                                                                                 |

| 7        | R/W        | I    | If the 6800-series MPU is connected:                                                                                                                                                                                                                                                      |

|          |            |      | Used as an input pin of read control signals (if R/W is high) or write control signals(if low).                                                                                                                                                                                           |

|          |            |      | If the 8080-series MPU is connected:                                                                                                                                                                                                                                                      |

|          |            |      | The /WR signal of the 8080-series MPU is entered in this pin. A signal on the data                                                                                                                                                                                                        |

|          |            |      | bus is fetched at the rising edge of /WR signal.                                                                                                                                                                                                                                          |

|          | A0         | I    | Usually connected to the low-order bit of the MPU address bus and used to identify the data or a command.                                                                                                                                                                                 |

|          |            |      | A0=0: DB0~DB7 are display control data.                                                                                                                                                                                                                                                   |

|          |            |      | A0=1: DB0~DB7 are display control data.                                                                                                                                                                                                                                                   |

| 9        | DB0        | I/O  | Tristate input/output pins. Connect these pins to an 8- or 16-bit microprocessor bus.                                                                                                                                                                                                     |

| 10       | DB1        | I/O  | Tristate input/output pins. Connect these pins to an 8- or 16-bit microprocessor bus.                                                                                                                                                                                                     |

| 11       | DB1<br>DB2 | I/O  | Tristate input/output pins. Connect these pins to an 8- or 16-bit microprocessor bus.                                                                                                                                                                                                     |

| <u> </u> | 002        | 1/ 0 | Instate input output pins. Connect these pins to an o- or To-bit fine opiocessor bus.                                                                                                                                                                                                     |

| 12 | DB3  | I/O | Tristate input/output pins. Connect these pins to an 8- or 16-bit microprocessor bus. |

|----|------|-----|---------------------------------------------------------------------------------------|

| 13 | DB4  | I/O | Tristate input/output pins. Connect these pins to an 8- or 16-bit microprocessor bus. |

| 14 | DB5  | I/O | Tristate input/output pins. Connect these pins to an 8- or 16-bit microprocessor bus. |

| 15 | DB6  | I/O | Tristate input/output pins. Connect these pins to an 8- or 16-bit microprocessor bus. |

| 16 | DB7  | I/O | Tristate input/output pins. Connect these pins to an 8- or 16-bit microprocessor bus. |

| 17 | LEDA | I   | LED anode (+5V)                                                                       |

| 18 | LEDK | I   | LED cathode (0V)                                                                      |

# 12.RELIABILITY

# **Content of Reliability Test**

|      |                                     | Environmental Test                                                                                                              |                        |                            |

|------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------|

| No.  | Test Item                           | Content of Test                                                                                                                 | Test Condition         | Applicable<br>Standard     |

| 1    | High temperature storage            | Endurance test applying the high storage temperature for a long time.                                                           | 80 ℃<br>200 hrs        |                            |

| 2    | Low temperature storage             | Endurance test applying the low storage temperature for a long time.                                                            | -30 ℃<br>200 hrs       |                            |

| 3    | High temperature operation          | Endurance test applying the electric stress (Voltage & Current) and the thermal stress to the element for a long time.          | 70 ℃<br>200 hrs        |                            |

| 4    | Low temperature operation           | Endurance test applying the electric stress under low temperature for a long time.                                              | -20 ℃<br>200 hrs       |                            |

| 5    | High temperature Humidity storage   | Endurance test applying the high temperature and high humidity storage for a long time.                                         | 50 ℃ , 90 RH<br>96 hrs | MIL-202E-103B<br>JIS-C5023 |

| 6    | High temperature Humidity operation | Endurance test applying the electric stress (Voltage & Current) and temperature humidity stress to the element for a long time. | 50 ℃ , 90 RH<br>96 hrs | MIL-202E-103B<br>JIS-C5023 |

| 7    | Temperature cycle                   | Endurance test applying the low and high temperature cycle.  -20°C                                                              | -20°C − 70°C 10 cycles |                            |

| Mech | anical Test                         |                                                                                                                                 |                        | I                          |

| 8    | Vibration test                      | Endurance test applying the vibration during transportation and using.                                                          | 10-22Hz → 1.5mmp-p     | MIL-202E-201A<br>JIS-C5025 |

|      |                                     |                                                                                                                                 | 22-500Hz →1.5G         | JIS-C7022-A-10             |

|      |                                     |                                                                                                                                 | Total 0.5hrs           |                            |

| 9    | Shock test         | Constructional and mechanical endurance test   | 50G half sign wave 1I | MIL-202E-213B   |

|------|--------------------|------------------------------------------------|-----------------------|-----------------|

|      |                    | applying the shock during transportation.      | msedc 3 times of each |                 |

|      |                    |                                                | direction             |                 |

| 10   | Atmospheric        | Endurance test applying the atmospheric        | 115 mbar 40 hrs       | MIL-202E-105C   |

|      | pressure test      | pressure during transportation by air.         |                       |                 |

| Othe | rs                 |                                                |                       |                 |

| 11   | Static electricity | Endurance test applying the electric stress to | VS=800V, RS=1.5 k     | MIL-883B-3015.1 |

|      | test               | the terminal.                                  | CS=100 pF             |                 |

|      |                    |                                                | 1 time                |                 |

<sup>\*\*\*</sup> Supply voltage for logic system = 3V. Supply voltage for LCD system = Operating voltage at 25°C.

# **Failure Judgement Criterion**

| Criterion Item            |   | Test Item No. |   |   |   |   |   |   |   |    |    | Failure Judgment Criterion          |

|---------------------------|---|---------------|---|---|---|---|---|---|---|----|----|-------------------------------------|

|                           | 1 | 2             | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |                                     |

| Basic specification       |   |               |   |   |   |   |   |   |   |    |    | Out of the Basic Specification      |

| Electrical characteristic |   |               |   |   |   |   |   |   |   |    |    | Out of the DC and AC Characterstic  |

| Mechanical                |   |               |   |   |   |   |   |   |   |    |    | Out of the Mechanical Specification |

| characterstic             |   |               |   |   |   |   |   |   |   |    |    | Color change : Out of Limit         |

|                           |   |               |   |   |   |   |   |   |   |    |    | Apperance Specification             |

| Optical characterstic     |   |               |   |   |   |   |   |   |   |    |    | Out of the Apperance Standard       |

# 13. QUALITY GUARANTEE

# **Acceptable Quality Level**

Each lot should satisfy the quality level defined as follows.

- Inspection method: MIL-STD-105E LEVEL II Normal one time sampling

- AQL

| Partition | AQL  | Definition                                                         |

|-----------|------|--------------------------------------------------------------------|

| A: Major  | 0.4% | Functional defective as product                                    |

| B: Minor  | 1.5% | Satisfy all functions as product but not satisfy cosmetic standard |

# **Definition of 'LOT'**

One lot means the delivery quantity to customer at one time.

# **Conditions of Cosmetic Inspection**

# **Environmental condition**

The inspection should be performed at the 1cm of height from the LCD module under 2 pieces of 40W white fluorescent lamps (Normal temperature  $20\sim25$  °C and normal humidity  $60 \pm 15$  %RH).

# **Inspection method**

The visual check should be performed vertically at more than 30cm distance from the LCD panel.

# **Driving voltage**

The VO value which the most optimal contrast can be obtained near the specified VO in the specification. (Within  $\pm 0.5$ V of typical value at 25°C.).

# 14. INSPECTION CRITERIA

# 14.1 Module Cosmetic Criteria

| No. | Item                  | Judgement Criterion                                        | Partition |  |

|-----|-----------------------|------------------------------------------------------------|-----------|--|

| 1   | Difference in Spec.   | None allowed                                               | Major     |  |

| 2   | Pattern peeling       | No substrate pattern peeling and floating                  | Major     |  |

| 3   | Soldering defects     | No soldering missing                                       | Major     |  |

|     |                       | No soldering bridge                                        | Major     |  |

|     |                       | No cold soldering                                          | Major     |  |

| 4   | Resist flaw on        | Invisible copper foil ('0.5mm or more) on substrate        |           |  |

| 4   | substrate             | pattern                                                    | Minor     |  |

| 5   | Accretion of metallic | No soldering dust No accretion of metallic foreign matters | Minor     |  |

|     | Foreign matter        | (Not exceed '0.2mm)                                        | Minor     |  |

| 6   | Stain                 | No stain to spoil cosmetic badly                           | Minor     |  |

| 7   | Plate discoloring     | No plate fading, rusting and discoloring                   | Minor     |  |

| 8   | Solder amount         | a. Soldering side of PCB                                   | Minor     |  |

|     |                       | Solder to form a 'Filet' all                               |           |  |

|     |                       | around the lead.                                           |           |  |

|     |                       | Solder should not hide the                                 |           |  |

|     | 1. Lead parts         | lead form perfectly. (too                                  |           |  |

|     |                       | much)                                                      |           |  |

|     |                       | b. Components side                                         |           |  |

|     |                       | (In case of 'Through Hole PCB')                            |           |  |

|     |                       |                                                            |           |  |

|     |                       | Solder to reach the Components side of PCB.                |           |  |

|     | 2. Flat packages      | Either 'Toe' (A) or 'Seal'                                 | Minor     |  |

|     |                       | (B) of the lead to be covered ABB                          |           |  |

|     |                       | by 'Filet'.                                                |           |  |

|     |                       |                                                            |           |  |

|     |                       | Lead form to be assume over solder. A B                    |           |  |

|     | 3. Chips              | $(3/2) H \geqslant h \geqslant (1/2) H$                    | Minor     |  |

|     |                       | ∫h ↓H                                                      |           |  |

|     |                       |                                                            |           |  |

|     | <u>l</u>              |                                                            |           |  |

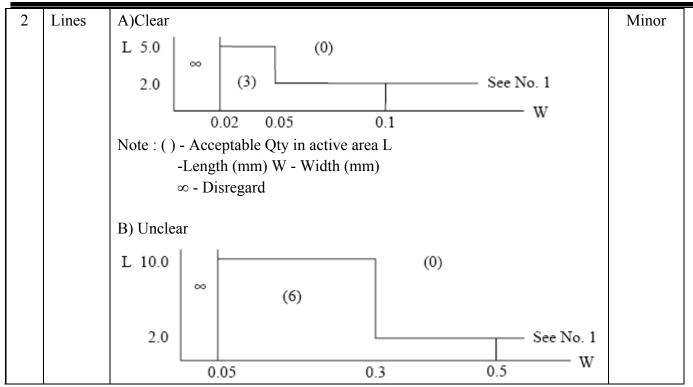

# 14.2 Screen Cosmetic Criteria (Non-Operating)

| No. | Defect               | Judgement Criterion                                                                                                                |                                                               | Partition |  |

|-----|----------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------|--|

| 1   | Spots                | In accordance with Screen                                                                                                          | Minor                                                         |           |  |

| 2   | Lines                | In accordance with Screen                                                                                                          | In accordance with Screen Cosmetic Criteria (Operating) No.2. |           |  |

| 3   | Bubbles in polarizer | Size : d mm<br>d ≤ 0.3                                                                                                             | Acceptable Qty in active area Disregard                       | Minor     |  |

|     | 1                    | $0.3 < d \le 1.0$                                                                                                                  | 3                                                             |           |  |

|     |                      | 1.0 < d ≤ 1.5<br>1.5 < d                                                                                                           | 1<br>0                                                        |           |  |

| 4   | Scratch              | In accordance with spots When the light reflects on to be remarkable.                                                              | Minor                                                         |           |  |

| 5   | Allowable density    | Above defects should be                                                                                                            | Minor                                                         |           |  |

| 6   | Coloration           | Not to be noticeable coloration in the viewing area of the LCD panels. Back-lit type should be judged with back-lit on state only. |                                                               |           |  |

| 7   | Contamination        | Not to be noticeable.                                                                                                              |                                                               |           |  |

# 14.3. Screen Cosmetic Criteria (Operating)

| No. | Defect | Judgement Criterion                                                                           |                               |  |

|-----|--------|-----------------------------------------------------------------------------------------------|-------------------------------|--|

| 1   | Spots  | A) Clear Note:                                                                                | Minor                         |  |

|     |        | Size : d mm                                                                                   |                               |  |

|     |        | d ≤ 0.1                                                                                       | Disregard                     |  |

|     |        | $0.1 < d \le 0.2$                                                                             | 3                             |  |

|     |        | $0.2 < d \le 0.3$                                                                             | 2                             |  |

|     |        | 0.3 < d                                                                                       | 0                             |  |

|     |        | Including pin holes and defective dots which must be within one pixel size.  B) Unclear Size: |                               |  |

|     |        | Size : d mm                                                                                   | Acceptable Qty in active area |  |

|     |        | d ≤ 0.2                                                                                       | Disregard                     |  |

|     |        | $0.2 < d \le 0.5$                                                                             | 6                             |  |

|     |        | $0.5 < d \le 0.7$                                                                             | 2                             |  |

|     |        | 0.7 < d                                                                                       | 0                             |  |

'Clear' = The shade and size are not changed by VO.

# 14.4. Screen Cosmetic Criteria (Operating) (Continued)

| No. | Defect            | Judgement Criterion                                                  | Partition |

|-----|-------------------|----------------------------------------------------------------------|-----------|

| 3   | Rubbing line      | Not to be noticeable.                                                |           |

| 4   | Allowable density | Above defects should be separated more than 10mm each other.         | Minor     |

| 5   | Rainbow           | Not to be noticeable.                                                | Minor     |

| 6   | Dot size          | To be 95% ~ 105% of the dot size (Typ.) in drawing. Partial          | Minor     |

|     |                   | defects of each dot (ex. pin-hole) should be treated as 'Spot'. (see |           |

|     |                   | Screen Cosmetic Criteria (Operating) No.1)                           |           |

| 7   | Uneven            | Uneven brightness must be BMAX / BMIN ≤ 2                            | Minor     |

|     | brightness (only  | - BMAX : Max. value by measure in 5 points                           |           |

|     | back-lit type     | - BMIN : Min. value by measure in 5 points                           |           |

|     | module)           | Divide active area into 4 vertically and horizontally. Measure       |           |

|     |                   | 5 points shown in the following figure.                              |           |

|     |                   |                                                                      |           |

|     |                   |                                                                      |           |

|     |                   |                                                                      |           |

|     |                   |                                                                      |           |

|     |                   | •                                                                    |           |

|     |                   |                                                                      |           |

|     |                   | 0 0                                                                  |           |

|     |                   |                                                                      |           |

|     |                   | O : Measuring points                                                 |           |

<sup>&#</sup>x27;Unclear' = The shade and size are changed by VO.

#### Note:

- (1) Size : d = (long length + short length) / 2

- (2) The limit samples for each item have priority.

- (3) Complexed defects are defined item by item, but if the number of defects are defined in above table, the total number should not exceed 10.

- (4) In case of 'concentration', even the spots or the lines of 'disregarded' size should not allowed. Following three situations should be treated as 'concentration'.

- 7 or over defects in circle of '5mm.

- 10 or over defects in circle of '10mm.

- 20 or over defects in circle of '20mm.

#### 15. PRECAUTIONS FOR USING LCD MODULES

### **Handing Precautions**

- (1) The display panel is made of glass. Do not subject it to a mechanical shock by dropping it or impact.

- (2) If the display panel is damaged and the liquid crystal substance leaks out, be sure not to get any in your mouth. If the substance contacts your skin or clothes, wash it off using soap and water.

- (3) Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary.

- (4) The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarizer carefully.

- (5) If the display surface becomes contaminated, breathe on the surface and gently wipe it with a soft dry cloth. If it is heavily contaminated, moisten cloth with one of the following solvents:

- Isopropyl alcohol

- Ethyl alcohol

- (6) Solvents other than those above-mentioned may damage the polarizer. Especially, do not use the following.

- Water

- Ketone

- Aromatic solvents

- (7) Exercise care to minimize corrosion of the electrode. Corrosion of the electrodes is accelerated by water droplets, moisture condensation or a current flow in a high-humidity environment.

- (8) Install the LCD Module by using the mounting holes. When mounting the LCD module make sure it is free of twisting, warping and distortion. In particular, do not forcibly pull or bend the IO cable or the backlight cable.

- (9) Do not attempt to disassemble or process the LCD module.

- (10) NC terminal should be open. Do not connect anything.

- (11) If the logic circuit power is off, do not apply the input signals.

- (12) To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

- Be sure to ground the body when handling the LCD modules.

- Tools required for assembling, such as soldering irons, must be properly grounded.

- To reduce the amount of static electricity generated, do not conduct assembling and other work under dry conditions.

- The LCD module is coated with a film to protect the display surface. Exercise care when peeling off this protective film since static electricity may be generated.

### **Storage Precautions**

When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps. Keep the modules in bags (avoid high temperature high humidity and low temperatures below 0 C). Whenever possible, the LCD modules should be stored in the same conditions in which they were shipped from our company.

#### **Others**

Liquid crystals solidify under low temperature (below the storage temperature range) leading to defective orientation or the generation of air bubbles (black or white). Air bubbles may also be generated if the module is subject to a low temperature.

If the LCD modules have been operating for a long time showing the same display patterns, the display patterns may remain on the screen as ghost images and a slight contrast irregularity may also appear. A normal operating status can be regained by suspending use for some time. It should be noted that this phenomenon does not adversely affect performance reliability.

To minimize the performance degradation of the LCD modules resulting from destruction caused by static electricity etc., exercise care to avoid holding the following sections when handling the modules.

- Exposed area of the printed circuit board.

- Terminal electrode sections.

# 16. USING LCD MODULES

### **Liquid Crystal Display Modules**

- LCD is composed of glass and polarizer. Pay attention to the following items when handling.

- (1) Please keep the temperature within specified range for use and storage. Polarization degradation, bubble generation or polarizer peel-off may occur with high temperature and high humidity.

- (2) Do not touch, push or rub the exposed polarizers with anything harder than an HB pencil lead (glass, tweezers, etc.).

- (3) N-hexane is recommended for cleaning the adhesives used to attach front/rear polarizers and reflectors made of organic substances which will be damaged by chemicals such as acetone, toluene, ethanol and isopropylalcohol.

- (4) When the display surface becomes dusty, wipe gently with absorbent cotton or other soft material like chamois soaked in petroleum benzin. Do not scrub hard to avoid damaging the display surface.

- (5) Wipe off saliva or water drops immediately, contact with water over a long period of time may cause deformation or color fading.

- (6) Avoid contacting oil and fats.

- (7) Condensation on the surface and contact with terminals due to cold will damage, stain or dirty the polarizers. After products are tested at low temperature they must be warmed up in a container before coming

is contacting with room temp erature air.

- (8) Do not put or attach anything on the display area to avoid leaving marks on.

- (9) Do not touch the display with bare hands. This will stain the display area and degradate insulation between terminals (some cosmetics are determinated to the polarizers).

- (10) As glass is fragile. It tends to become or chipped during handling especially on the edges. Please avoid dropping or jarring.

# **Installing LCD Modules**

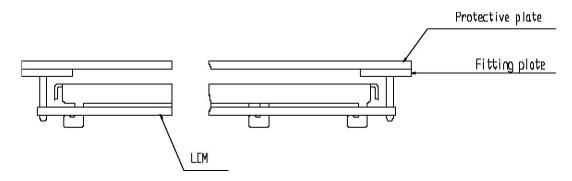

The hole in the printed circuit board is used to fix LCM as shown in the picture below. Attend to the following items when installing the LCM.

(1) Cover the surface with a transparent protective plate to protect the polarizer and LC cell.

(2) When assembling the LCM into other equipment, the spacer to the bit between the LCM and the fitting plate should have enough height to avoid causing stress to the module surface, refer to the individual specifications for measurements. The measurement tolerance should be 0.1mm.

### **Precaution for Handing LCD Modules**

Since LCM has been assembled and adjusted with a high degree of precision, avoid applying excessive shocks to the module or making any alterations or modifications to it.

- (1) Do not alter, modify or change the the shape of the tab on the metal frame.

- (2) Do not make extra holes on the printed circuit board, modify its shape or change the positions of components to be attached.

- (3) Do not damage or modify the pattern writing on the printed circuit board.

- (4) Absolutely do not modify the zebra rubber strip (conductive rubber) or heat seal connector.

- (5) Except for soldering the interface, do not make any alterations or modifications with a soldering iron.

- (6) Do not drop, bend or twist LCM.

# **Electro-Static Discharge Control**

Since this module uses a CMOS LSI, the same careful attention should be paid to electrostatic discharge as for an ordinary CMOS IC.

- (1) Make certain that you are grounded when handing LCM.

- (2) Before remove LCM from its packing case or incorporating it into a set, be sure the module and your body have the same electric potential.

- (3) When soldering the terminal of LCM, make certain the AC power source for the soldering iron does not

leak.

- (4) When using an electric screwdriver to attach LCM, the screwdriver should be of ground potentiality to minimize as much as possible any transmission of electromagnetic waves produced sparks coming from the commutator of the motor.

- (5) As far as possible make the electric potential of your work clothes and that of the work bench the ground potential.

- (6) To reduce the generation of static electricity be careful that the air in the work is not too dried. A relative humidity of 50%60% is recommended.

### Precaution for soldering to the LCM

(1) Observe the following when soldering lead wire, connector cable and etc. to the LCM.

- Soldering iron temperature : 280 C 10 C.

Soldering time : 3-4 sec.Solder : eutectic solder.

If soldering flux is used, be sure to remove any remaining flux after finishing to soldering operation. (This does not apply in the case of a non-halogen type of flux.) It is recommended that you protect the LCD surface with a cover during soldering to prevent any damage dur to flux spatters.

- (2) When soldering the electroluminescent panel and PC board, the panel and board should not be detached more than three times. This maximum number is determined by the temperature and time conditions mentioned above, though there may be some variance depending on the temperature of the soldering iron.

- (3) When remove the electoluminescent panel from the PC board, be sure the solder has completely melted, the soldered pad on the PC board could be damaged.

### **Precautions for Operation**

- (1) Viewing angle varies with the change of liquid crystal driving voltage (VO). Adjust VO to show the best contrast.

- (2) Driving the LCD in the voltage above the limit shortens its life.

- (3) Response time is greatly delayed at temperature below the operating temperature range. However, this does not mean the LCD will be out of the order. It will recover when it returns to the specified temperature range.

- (4) If the display area is pushed hard during operation, the display will become abnormal. However, it will return to normal if it is turned off and then back on.

- (5) Condensation on terminals can cause an electrochemical reaction disrupting the terminal circuit. Therefore, it must be used under the relative condition of 40 °C , 50% RH.

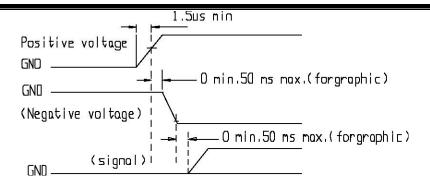

- (6) When turning the power on, input each signal after the positive/negative voltage becomes stable.

### **Storage**

When storing LCDs as spares for some years, the following precaution are necessary.

- (1) Store them in a sealed polyethylene bag. If properly sealed, there is no need for dessicant.

- (2) Store them in a dark place. Do not expose to sunlight or fluorescent light, keep the temperature between 0 C and 35 C.

- (3) The polarizer surface should not come in contact with any other objects. (We advise you to store them in the container in which they were shipped.)

#### Safety

- (1) It is recommended to crush damaged or unnecessary LCDs into pieces and wash them off with solvents such as acetone and ethanol, which should later be burned.

- (2) If any liquid leakes out of a damaged glass cell and comes in contact with the hands, wash off thoroughly with soap and water.

### **Return LCM under warranty**

No warranty can be granted if the precautions stated above have been disregarded. The typical examples of violations are :

- Broken LCD glass.

- PCB eyelet's damaged or modified.

- PCB conductors damaged.

- Circuit modified in any way, including addition of components.

- PCB tampered with by grinding, engraving or painting varnish.

- soldering to or modifying the bezel in any manner.

Module repairs will be invoiced to the customer upon mutual agreement. Modules must be returned with sufficient description of the failures or defects. Any connectors or cable installed by the customer must be removed completely without damaging the PCB eyelet's, conductors and terminals.

# 液晶显示模块使用注意事项

- 1. 请勿随意自行加工、整修、拆卸。

- 2. 避免对液晶屏表面施加压力。

- 3. 不要用手随意去摸外引线、电路板上的电路及金属框。

- 4. 如必须直接接触时,应使人体与模块保持同一电位,或将人体良好接地。

- 5. 焊接使用的烙铁、操作用的电动改锥等工具必须良好接地,没漏电。

- 6. 严防各种静电。

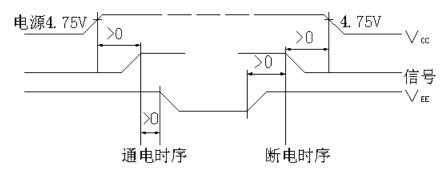

- 7. 模块使用接入电源及断开电源时,必须按图时序进行。即必须在正电源(5±0.25V) 稳定接入后,才能输入信号电平。如在电源稳定接入前,或断开后就输入信号电平, 将会损坏模块中的集成电路,使模块损坏。

- 8. 点阵模块在调节时,应调整 VEE 至最佳对比度、视角时为止。如果 VEE 调整过高,不仅会影响显示,还会缩短液晶的寿命。

- 9. 模块表面结雾时,不要通电工作,因为这将引起电极化学反应,产生断线。

- 10. 模块要存储在暗处(避阳光),温度在-10℃~+35℃,湿度在 RH60%以上的地方。 如能装入聚乙烯口袋(最好有防静电涂层)并将口封住最好。

以上使用说明由北京中显电子有限公司编制,有问题请电话联络,我们将竭诚为您服务,同时,提供完善的保修服务!因为每种液晶使用的控制器都不一样,控制器的型号基本就决定了液晶的指令形式和使用方式,所以,在说明书里一般不会详细照搬控制器说明书的每个细节,只会简要介绍常用指令,如果需要了解详细的指令和具体电气参数,请参照WWW.ZXLCD.COM网站里的"技术支持"菜单下,均有对应控制器手册免费下载,直接对应现有各类液晶使用的各种控制器,使用手册里一般有具体电气参数说明,指令详细介绍,同时辅以编程实例,以便客户详细参照,同时提高编程及操作技巧。

服务电话: 010-52926620,82626833

公司地址:北京市中关村大街32号蓝天和盛大厦811室